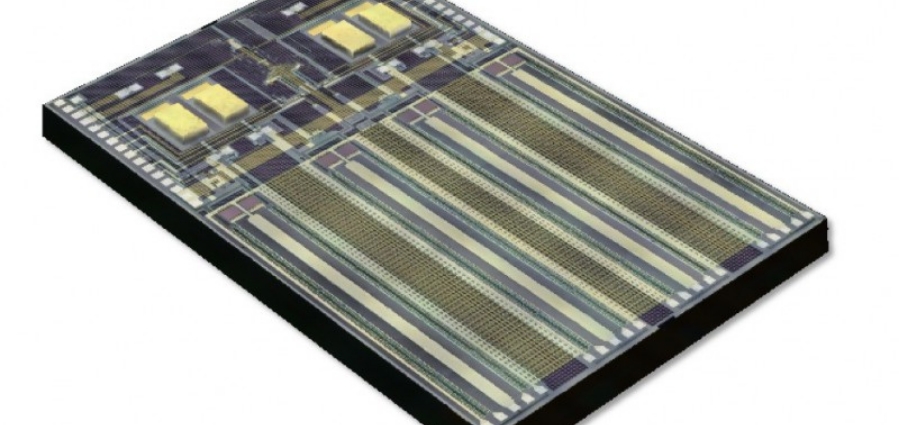

Silicon photonics integrated chip: Integration of photons and electrons...

Against the backdrop of exponential growth in data center traffic and surging demand for high-speed, low-power transmission in 5G/6G communications, silicon photonic integrated chips have become a key technology to break through the bottlenecks of traditional electrical interconnections by deeply integrating photons and electrons. Unlike traditional discrete optoelectronic devices, silicon photonic integrated chips integrate optical functional units such as lasers, modulators, and detectors with silicon-based CMOS circuits on a single chip, achieving Tbps-level data transmission rates and sub-picojoule/bit ultra-low power consumption, providing new solutions for cloud computing, high-performance computing, and other fields. Based on industrial practice and cutting-edge research, this article analyzes the core advantages, technological breakthroughs, and application challenges of silicon photonic integrated chips.

Core Technical Advantages: Disrupting the Performance Limits of Traditional Electrical Interconnections

1. Ultra-High Speed and Low Power Transmission

Tbps-level data transmission:

Intel's 400G silicon photonic transceiver module achieves 4×100Gbps data transmission over a single fiber using wavelength division multiplexing (WDM) technology, with a transmission distance of 2km. This is a 16-fold increase in speed compared to traditional electrical interconnections (up to 25Gbps), meeting the demand for high-speed interconnection between racks in data centers.

Significant reduction in energy consumption:

The drive power consumption of silicon photonic modulators is as low as 1.5pJ/bit, only 1/10 of that of traditional electrical modulators (10-20pJ/bit). Broadcom's silicon photonic switch chip consumes only 30W at a transmission rate of 1.6Tbps, a 40% reduction compared to all-electrical solutions, effectively alleviating the heat dissipation pressure in data centers.

2. High-Density Integration and Cost Advantages

Chip-level integration:

Based on 28nm CMOS technology, TSMC integrates 16 optical channels and driver circuits on a 10mm×10mm chip, with an integration density 100 times that of traditional optical modules. This high-density integration reduces the cost of optical interconnection to **$0.1/Gbps/km**, a 70% reduction compared to discrete optical device solutions.

Compatibility with CMOS processes:

Silicon photonic chips can be directly manufactured using mature CMOS production lines, with a yield rate of over 90%. Luxtera's silicon photonic chips, using TSMC's 16nm process, have a single-chip cost controlled within $50, accelerating their large-scale deployment in 5G fronthaul networks.

Key Technological Breakthroughs: Synergistic Innovation in Materials and Processes

1. R&D of New Optoelectronic Devices

Breakthrough in silicon-based lasers:

Belgium's imec has achieved room-temperature continuous-wave output power of 5mW for silicon-based lasers through heterogeneous integration of III-V semiconductor materials, with a side-mode suppression ratio **>30dB**, solving the problem of low luminous efficiency of silicon materials and promoting the monolithic integration of silicon photonic chips.

Optimization of high-speed modulators:

The microring modulator developed by the Massachusetts Institute of Technology (MIT), using silicon-germanium (SiGe) materials, has increased the modulation rate to 100Gbps, reduced the half-wave voltage to 1V, and shortened the response time to 1ps, providing key device support for 6G terahertz communications.

2. Innovation in Integration Processes

Hybrid integration technology:

Huawei uses flip-chip technology to bond III-V lasers with silicon photonic chips, achieving an alignment accuracy of 0.1μm and an optical coupling efficiency **>70%**. This has been applied to its 400G coherent optical modules, with a bit error rate below 10⁻¹².

3D heterogeneous integration:

STMicroelectronics' silicon photonic chips vertically integrate optical modules with power management and signal processing circuits through 3D stacking technology, reducing the overall size by 60%. Applied in automotive lidar systems, the data processing latency is reduced to 50ns.

Diversified Application Scenarios: Reshaping the Communication and Computing Ecosystem

1. Data Centers and Cloud Computing

High-speed interconnection between racks:

The silicon photonic switches deployed in Microsoft Azure's data centers achieve a switching capacity of 200Tbps, reducing network latency from 10μs to 1μs, increasing cluster computing efficiency by 25%, and saving **$50 million** in annual operating costs.

AI computing power acceleration:

Google's TPU v4 uses silicon photonic interconnection technology to achieve 100GB/s data transmission bandwidth between 1024 computing units, increasing the AI model training speed by 30% and facilitating the rapid iteration of large language models.

2. 5G/6G Communication Networks

Fronthaul and midhaul links:

ZTE's 5G base station silicon photonic modules achieve 25Gbps×8-channel parallel transmission over a 20km transmission distance, with a power consumption of only 3W. Replacing traditional copper cable solutions reduces energy consumption per station by 40% and construction costs by 35%.

Future 6G terahertz communications:

Samsung's silicon photonic terahertz transmitter achieves 10Gbps data transmission in the 200GHz band, and with beamforming technology, the communication distance reaches 100m, providing a new direction for 6G wireless communications.

3. Biomedical and Sensing Fields

Integrated optical biosensors:

The silicon photonic biochip developed by Stanford University can detect COVID-19 antibodies within 10 minutes using surface plasmon resonance (SPR) technology, with a detection limit of 10⁻¹² M, and a cost only 1/10 of traditional equipment.

Fiber optic sensing systems:

GE's silicon photonic fiber optic sensors are used to monitor the temperature of gas turbine blades, with a resolution of 0.1℃ and a response time **<1ms**, providing early warning of equipment failures and reducing downtime by 20%.

Existing Challenges and Development Directions

1. Performance Bottlenecks of Optoelectronic Devices

Challenges: The output power of silicon-based lasers is still insufficient (usually < 10mW), limiting transmission distance; the bandwidth of modulators is difficult to exceed 100Gbps, failing to meet future demand for rates of 1.6T and above.

Solutions:

Explore the integration of 2D materials (such as graphene and black phosphorus) with silicon, aiming to increase laser power to 50mW;

Develop micro-nano structured modulators, using quantum confinement effects to expand bandwidth to 200Gbps.

2. High Complexity of Integration Processes

Challenges: Optoelectronic hybrid integration involves a variety of materials and processes, leading to large fluctuations in manufacturing yield, and the single-chip cost is still 2-3 times higher than that of traditional electrical chips.

Solutions:

Promote standardized IP modules, shortening the development cycle by 30%;

Optimize heterogeneous integration processes, increasing the yield rate from 90% to **95%** or above.

3. System-Level Design Challenges

Challenges: Poor interface compatibility between silicon photonic chips and existing electrical systems, and immature optical signal processing algorithms, limiting large-scale commercialization.

Solutions:

Formulate unified optical interconnection interface standards, such as the Co-Packaged Optics (CPO) specification promoted by the Optical Internetworking Forum (OIF);

Develop AI-assisted optical signal processing algorithms, increasing the system's bit error rate tolerance by 20dB.

As a cutting-edge technology integrating photons and electrons, silicon photonic integrated chips are moving from the laboratory to industrial applications. Driven by the data flood and demand for high-speed communications, with material innovation, process optimization, and ecosystem improvement, silicon photonic chips are expected to become the core devices of the next-generation information infrastructure, driving computing, communication, and sensing technologies toward higher performance and lower power consumption.